Digital Security Lock System (Hardware Logic Design)

تفاصيل العمل

Project Overview:

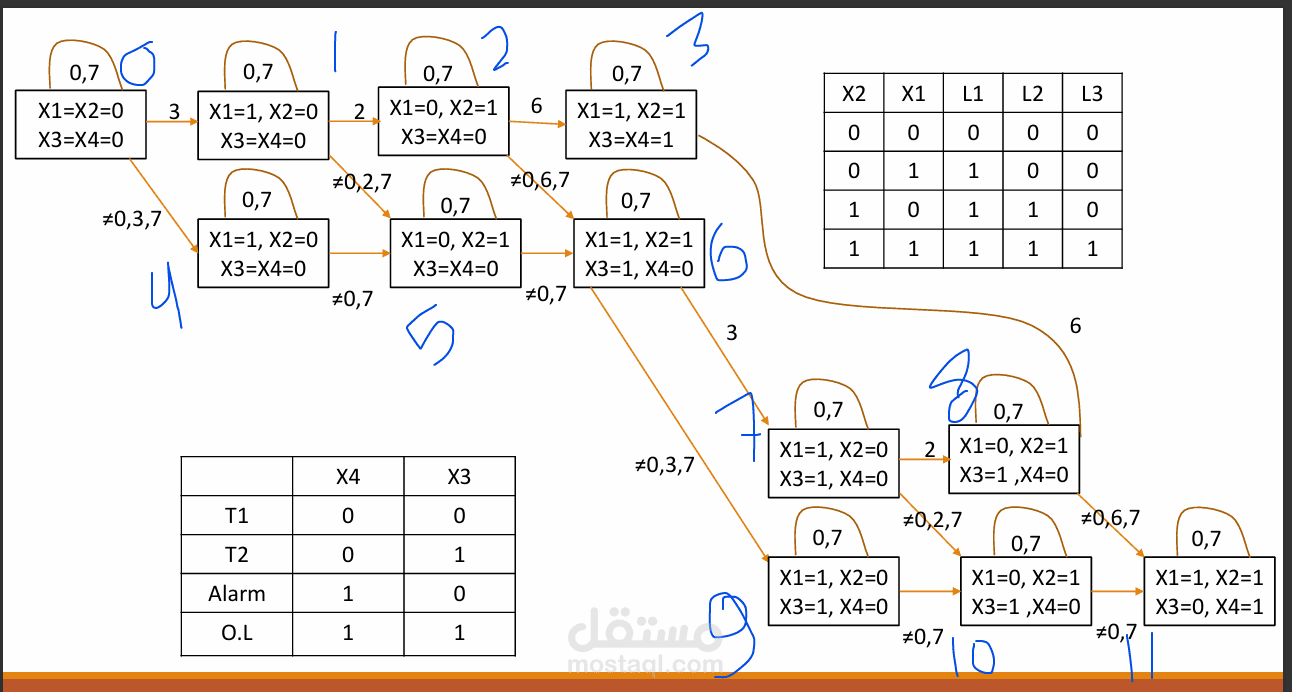

A sophisticated hardware-based security locking mechanism designed using discrete logic components and memory ICs. Unlike software-based systems, this project relies entirely on sequential and combinational digital logic to verify credentials.

Key Technical Features:

Input Encoding: Utilized a 74HC148 Priority Encoder to convert decimal keypad inputs into binary format for processing.

Memory & Storage: Integrated a 2732 EPROM/Memory chip to store and compare the pre-defined security password (163).

Data Synchronization: Employed 74HC374 D-type Flip-Flops as latches to hold and synchronize data states during the verification process.

Visual Interface: Integrated a 7447 BCD to 7-Segment Decoder to drive the display, providing real-time visual feedback of the entered digits.

Status Indicators: Designed a multi-stage alert system using Red LEDs and a Buzzer (BUZ2) for audible feedback upon successful or failed entry.

Technical Stack:

Logic Components: 74HC148, 74HC138 (Decoder), 74HC374 (Flip-Flops), 74HC08 (AND Gates).

Memory: 2732 EPROM.

Simulation & Design: Proteus Professional.