تصميم SPI Slave باستخدام Verilog HDL

تفاصيل العمل

تصميم SPI Slave باستخدام Verilog HDL

تصميم Finite State Machine بترميز Gray Code

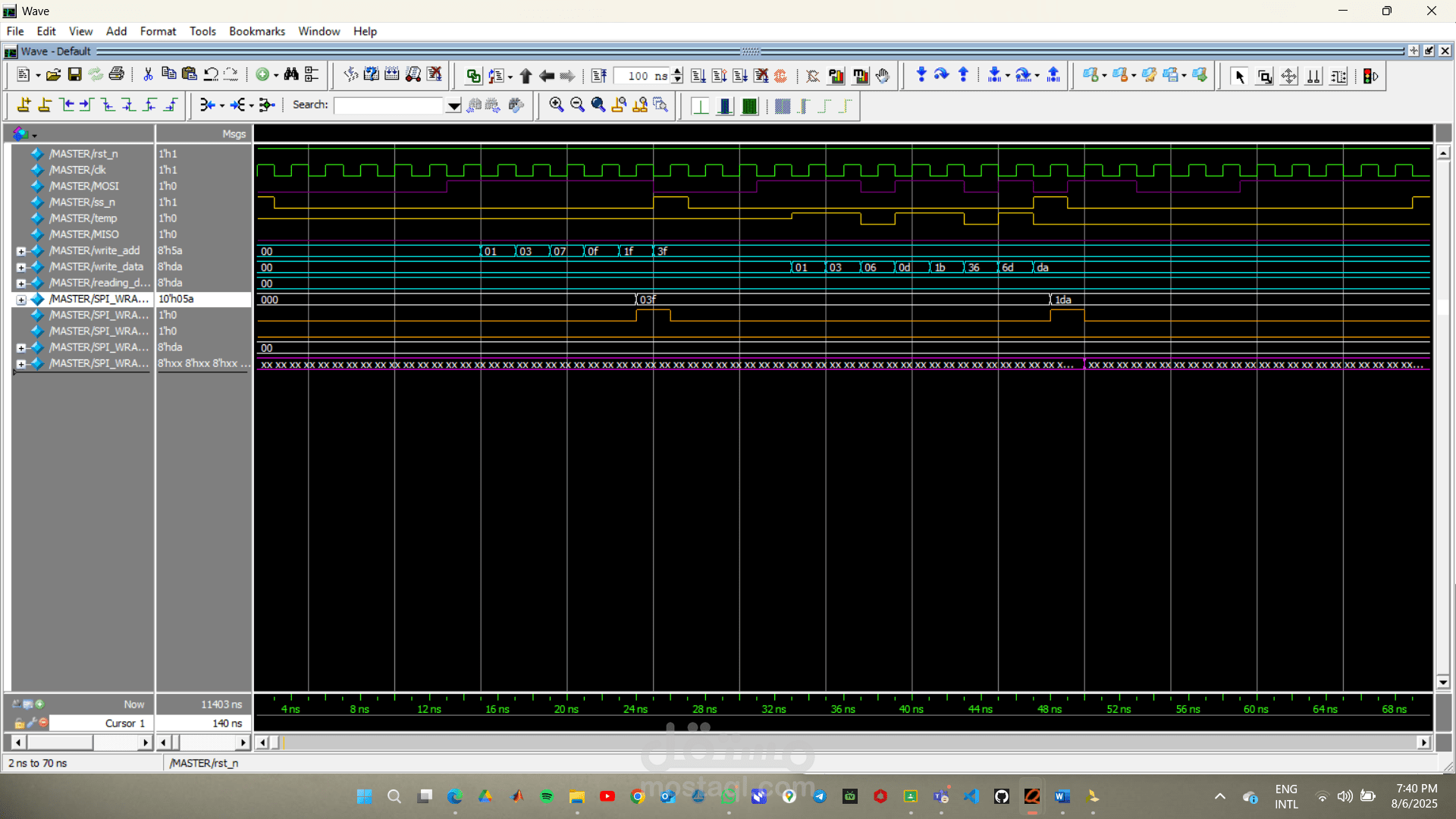

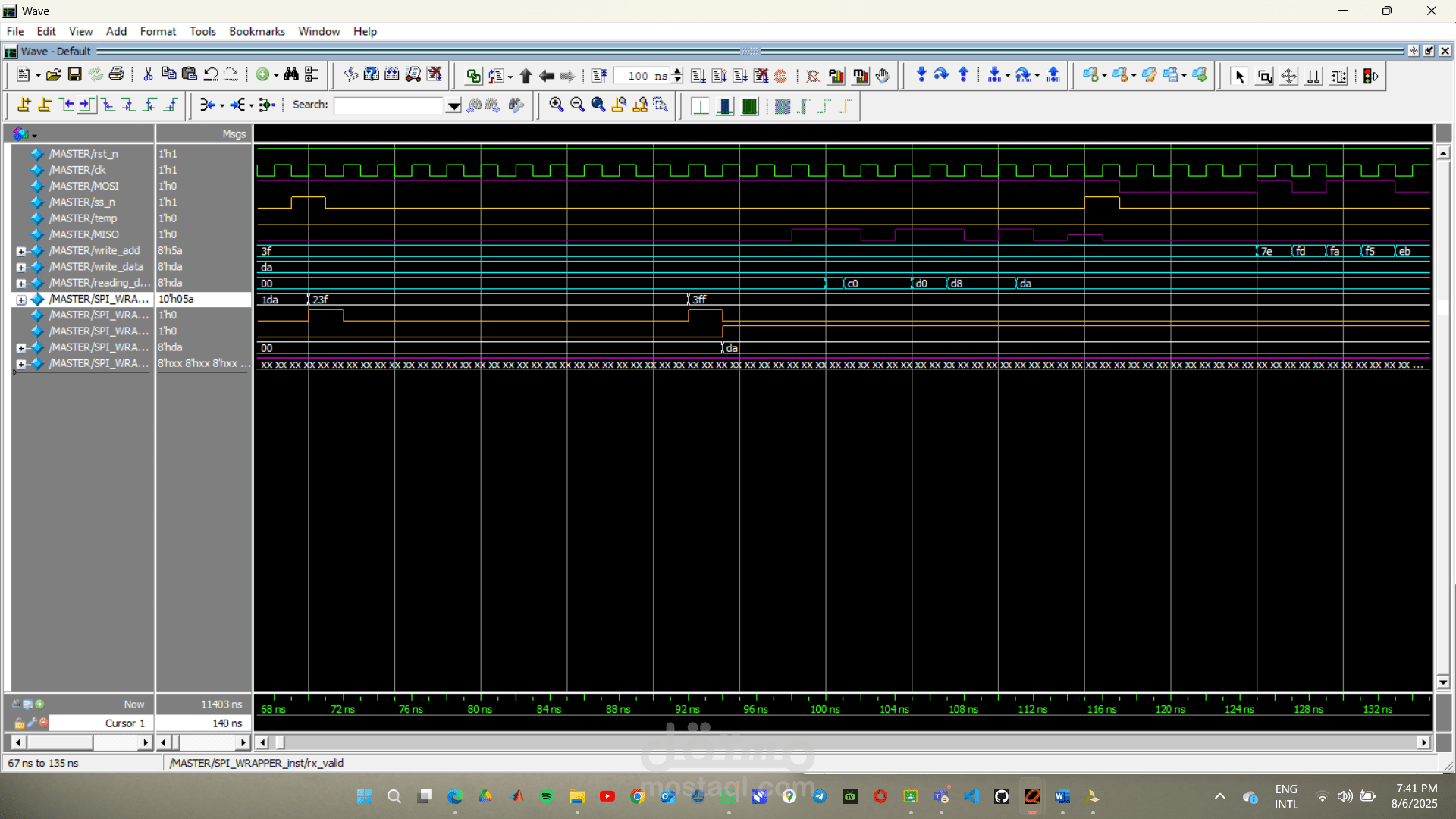

تحليل بروتوكول SPI وتنفيذ طبقة التحكم بالكامل

تنفيذ أوامر Write و Read Address و Read Data

تصميم Shift Registers لاستقبال وإرسال البيانات

توليد إشارات rx_valid و tx_valid للتحكم في نقل البيانات

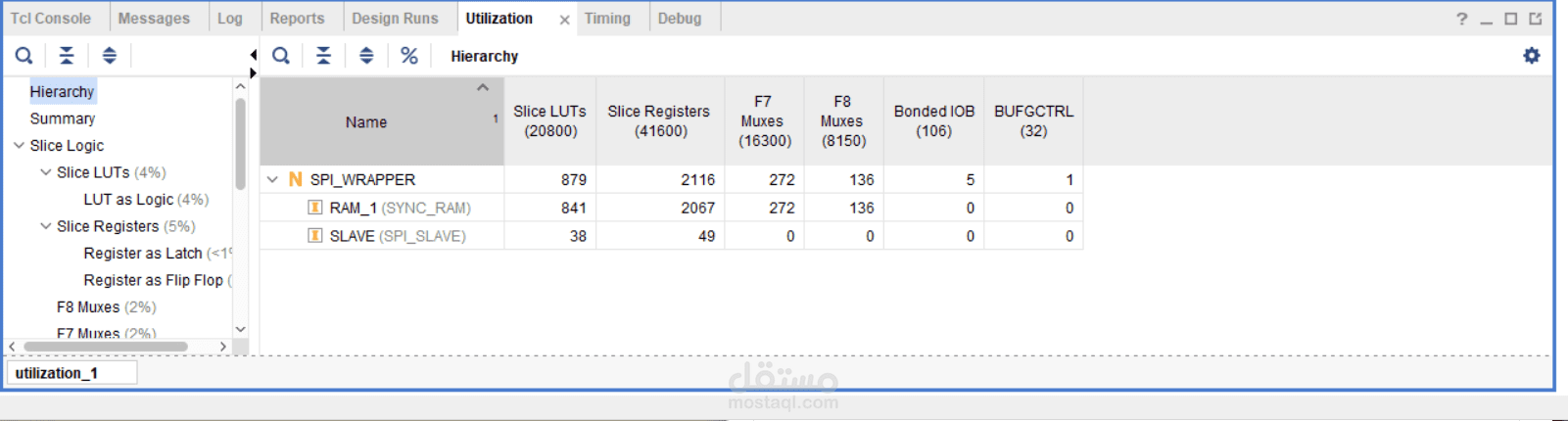

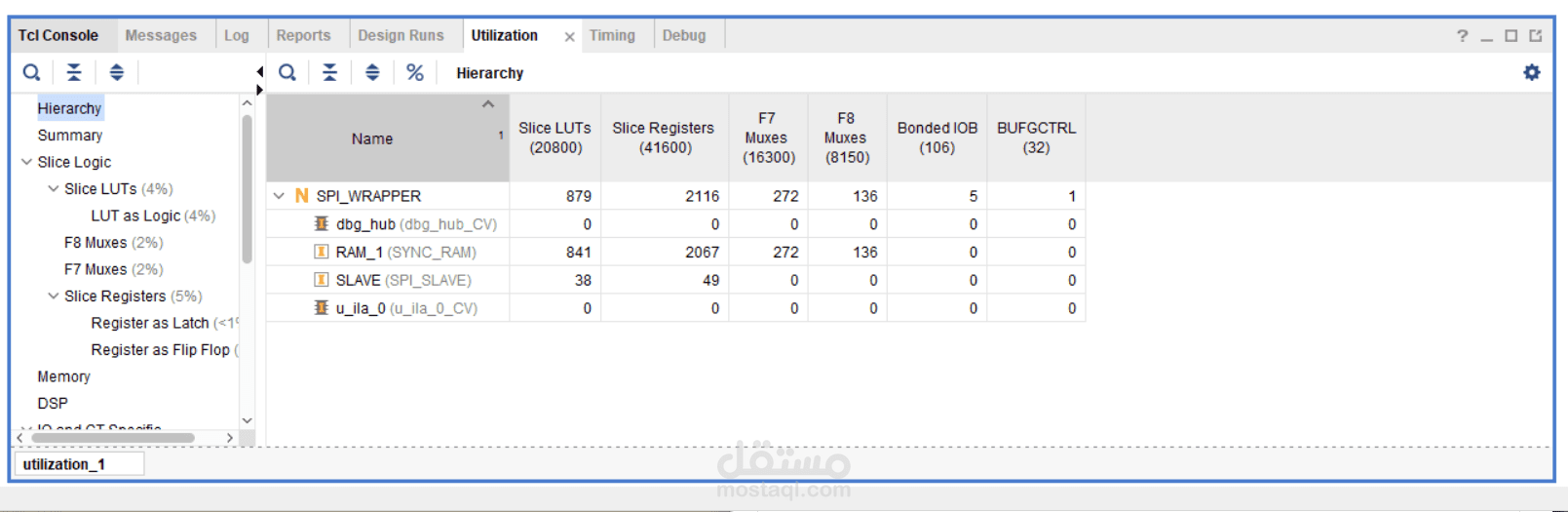

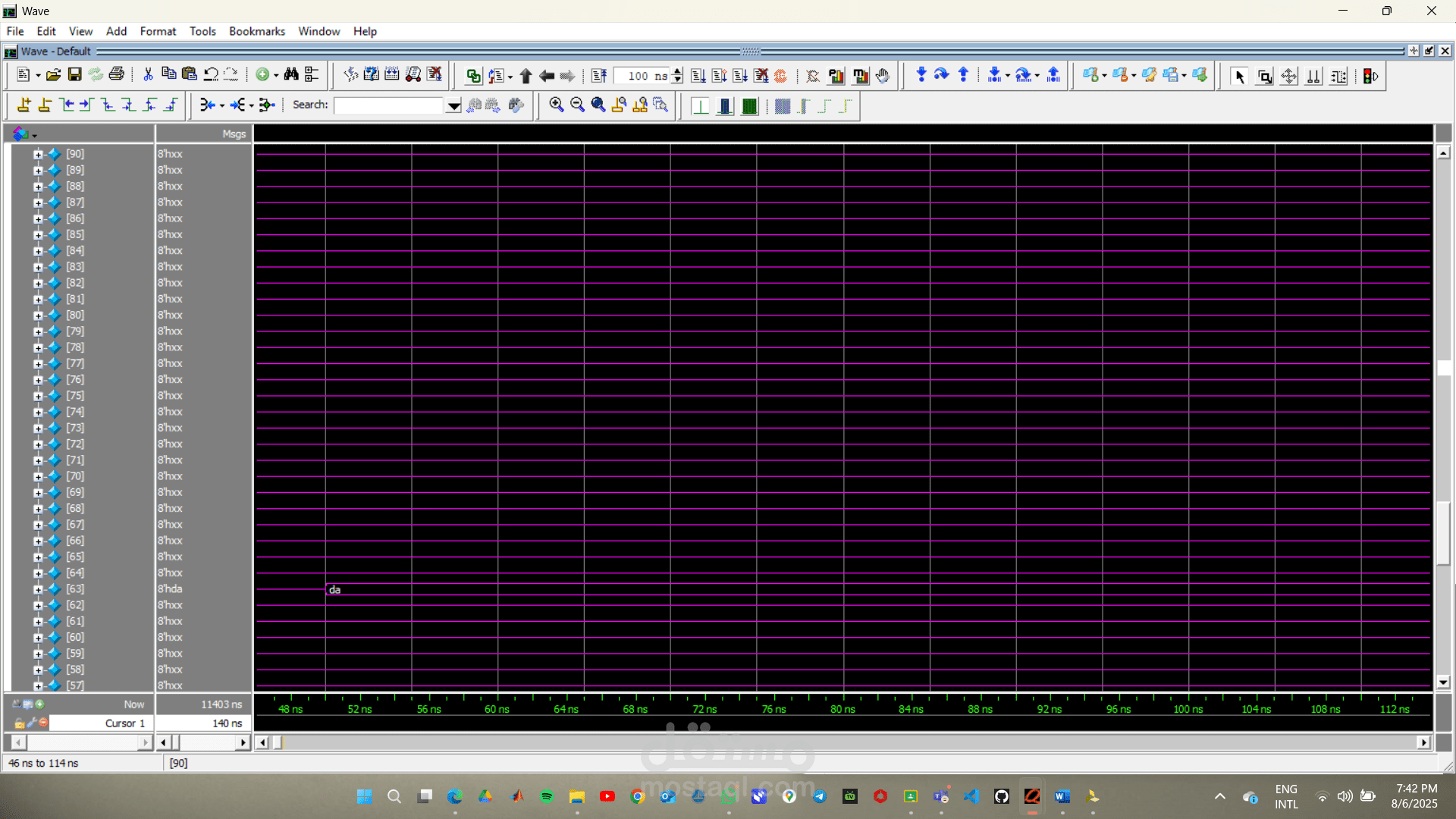

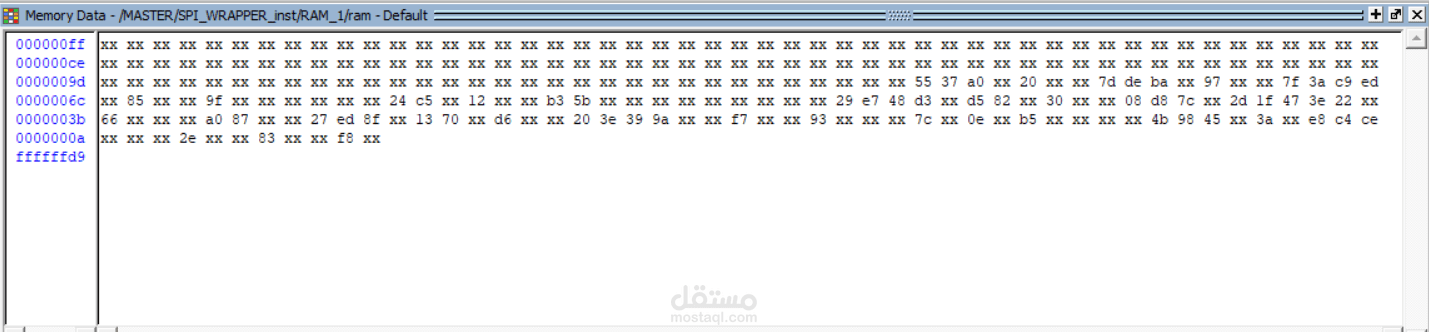

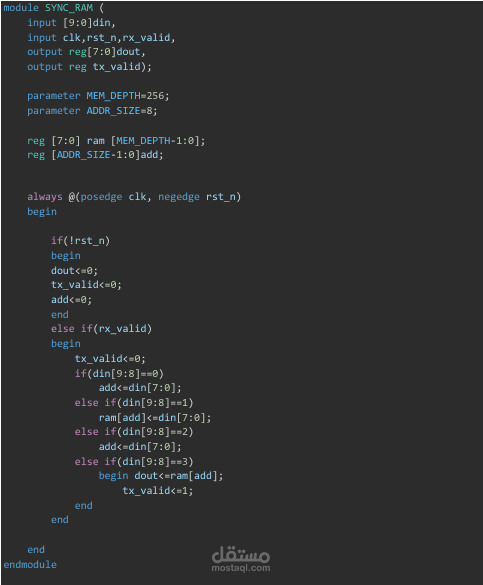

تصميم Synchronous RAM بعمق 256 موقع تخزين

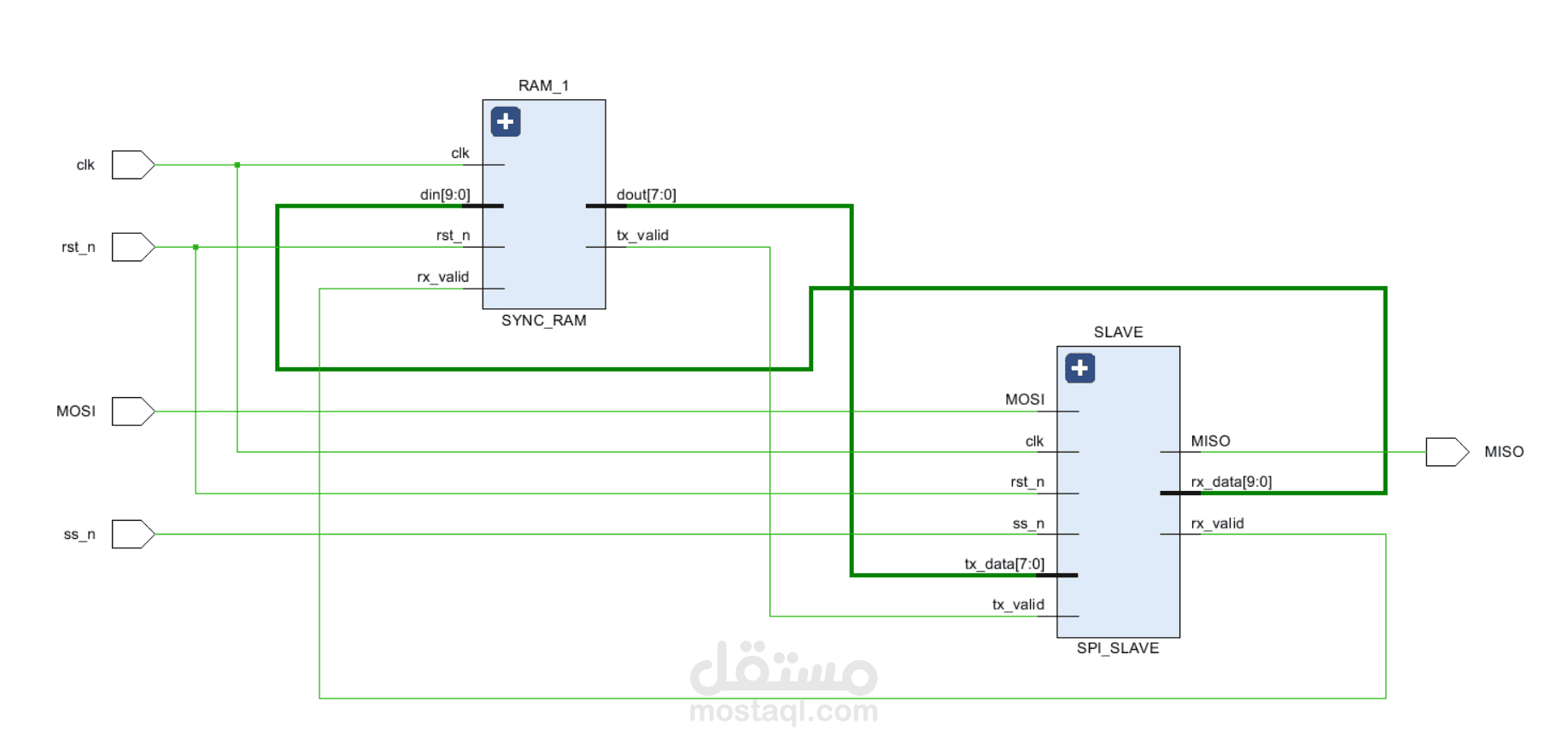

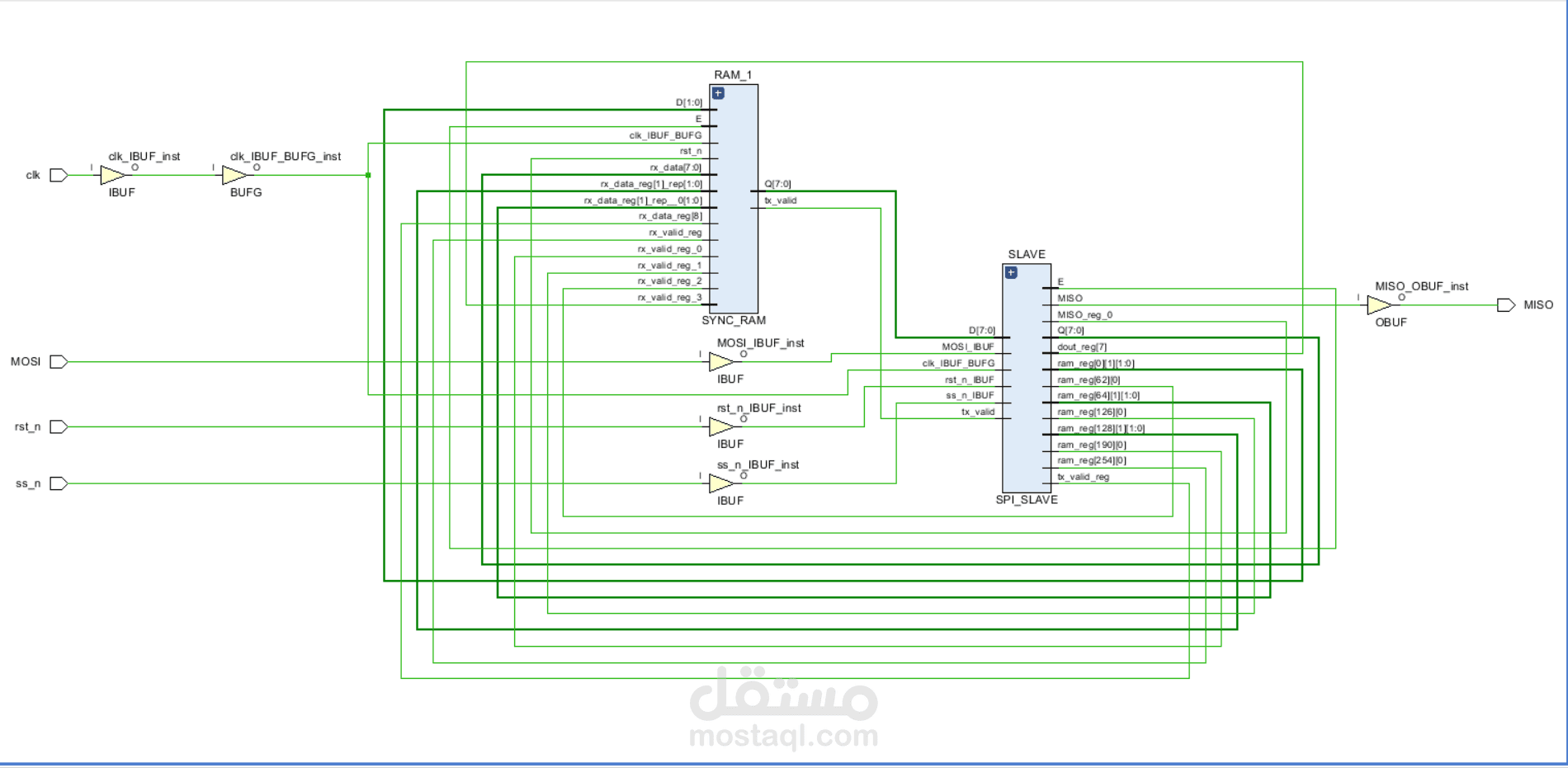

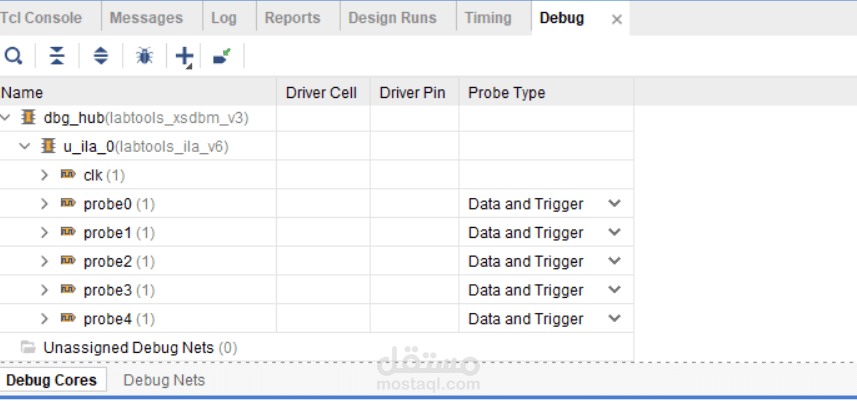

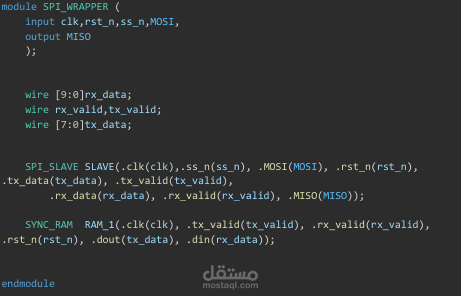

ربط SPI Slave مع RAM من خلال Wrapper Module

تطوير Testbench يحاكي سلوك SPI Master

توليد Stimulus عشوائي لاختبار جميع الحالات المحتملة

التحقق من صحة البيانات باستخدام Self Checking Mechanism

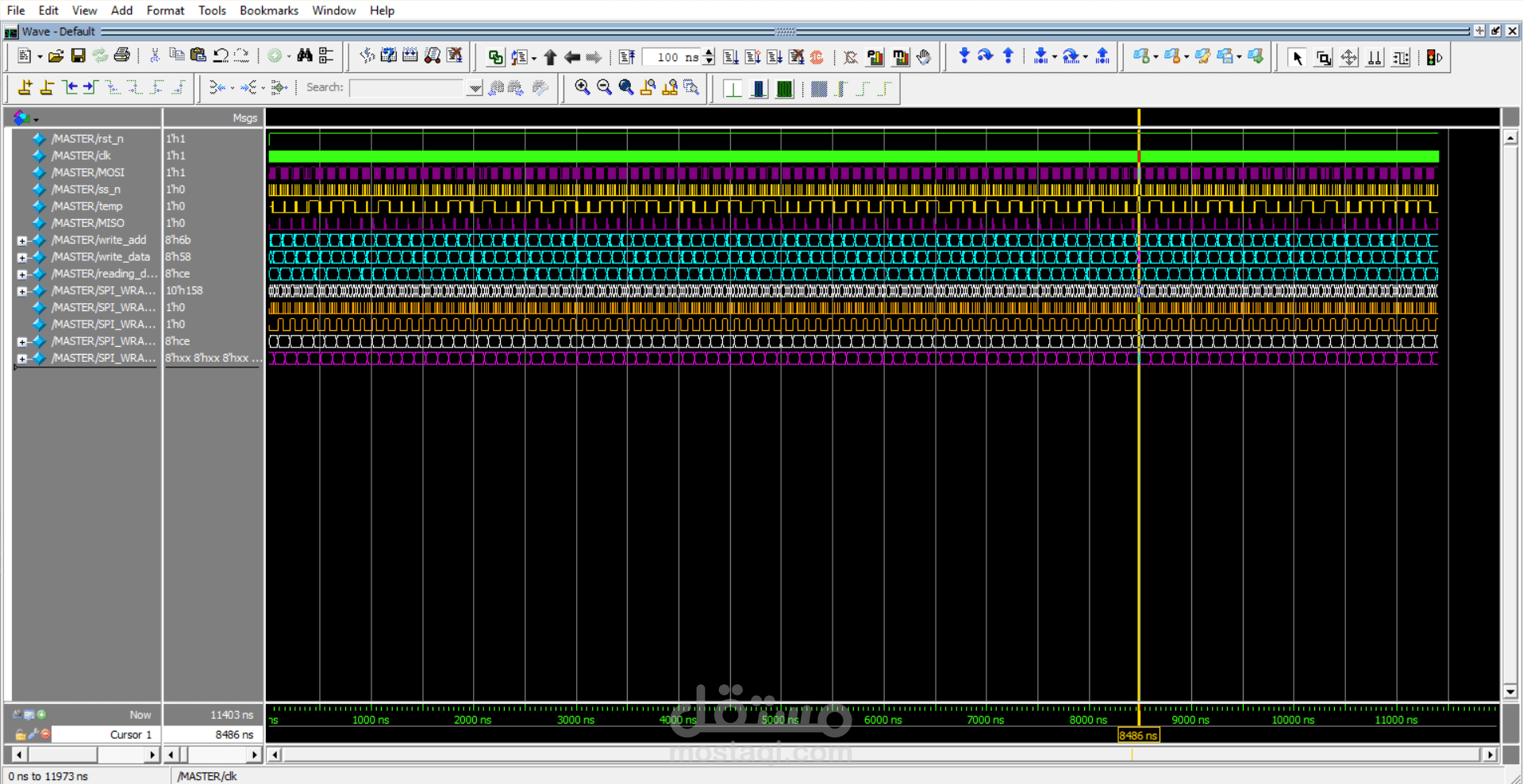

تحليل نتائج المحاكاة واكتشاف الأخطاء وتصحيحها

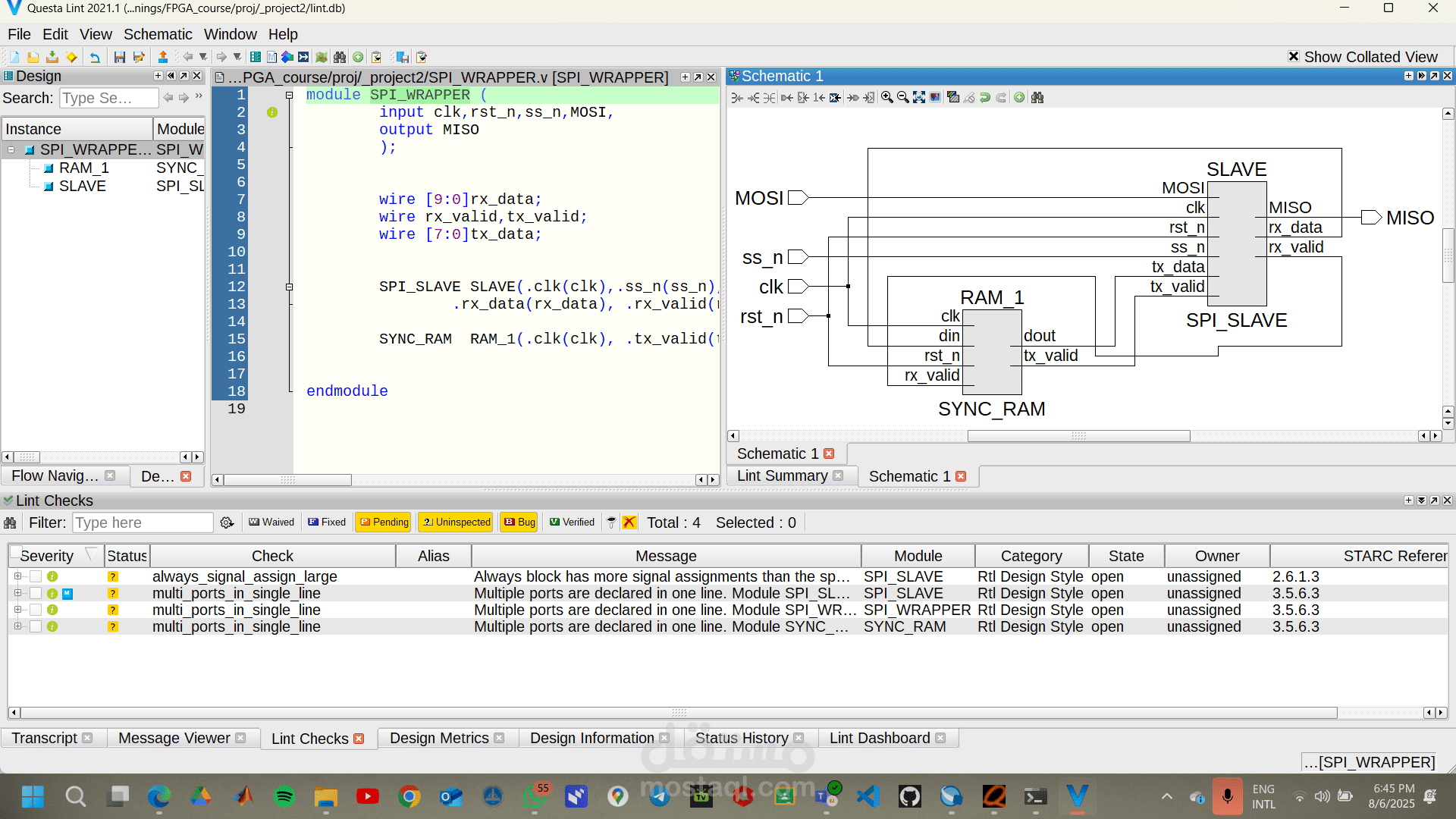

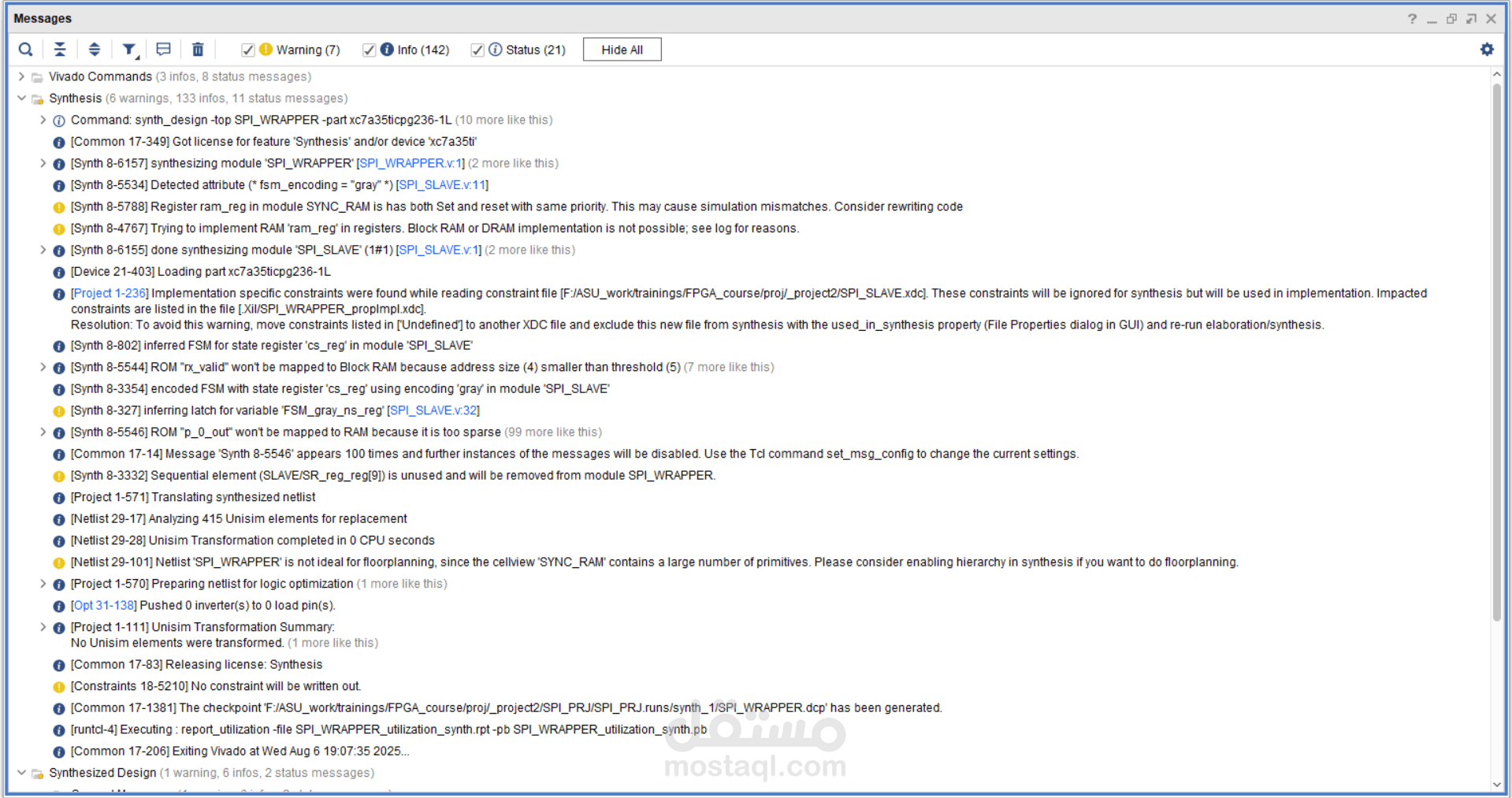

تنفيذ Linting لتحسين جودة الكود وتقليل الأخطاء

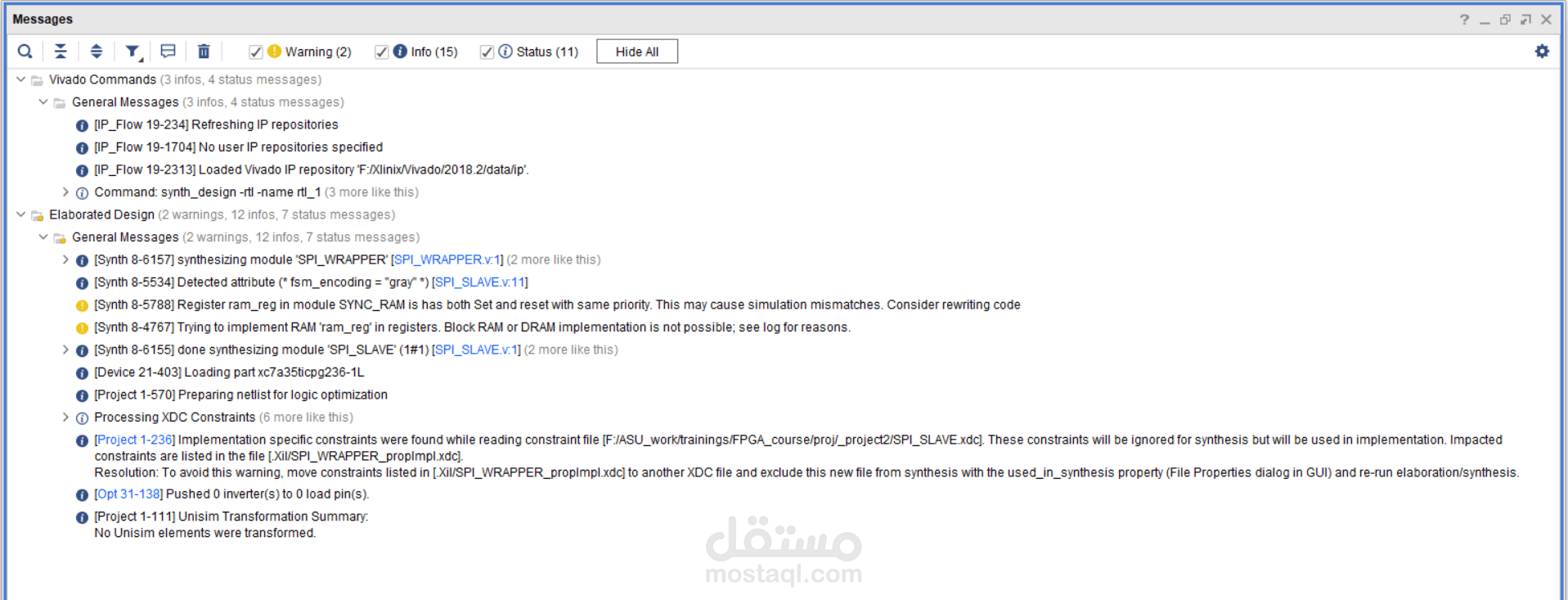

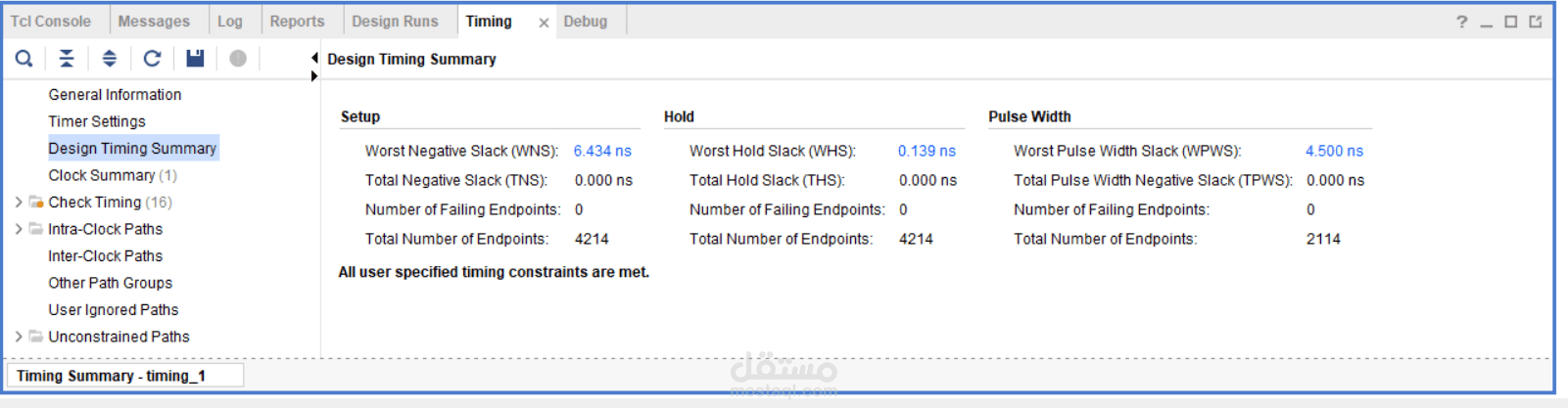

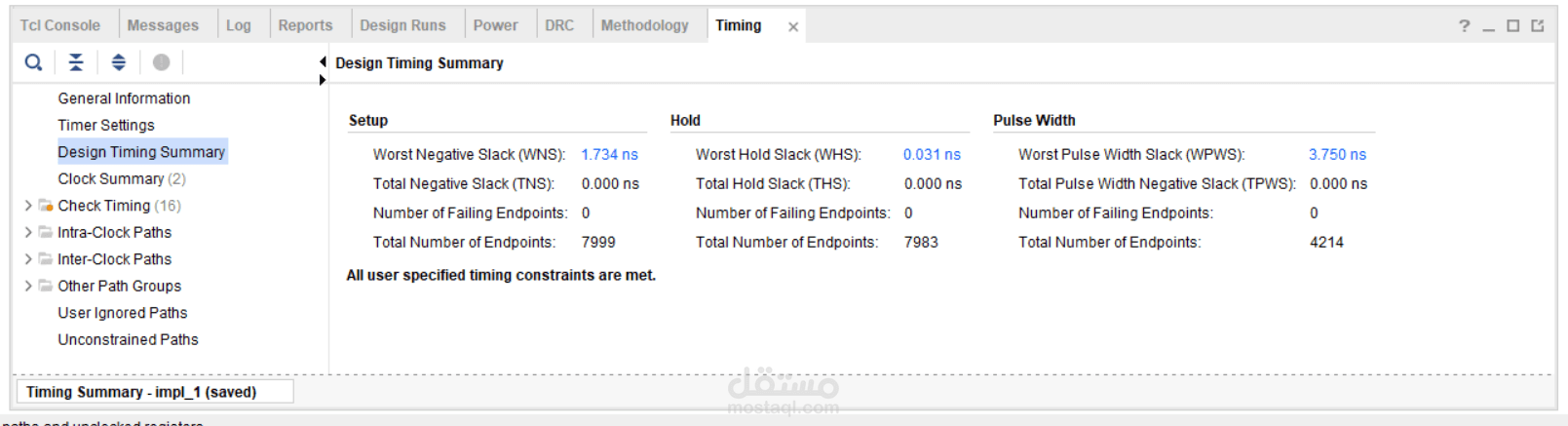

قياس كفاءة التصميم بعد Synthesis

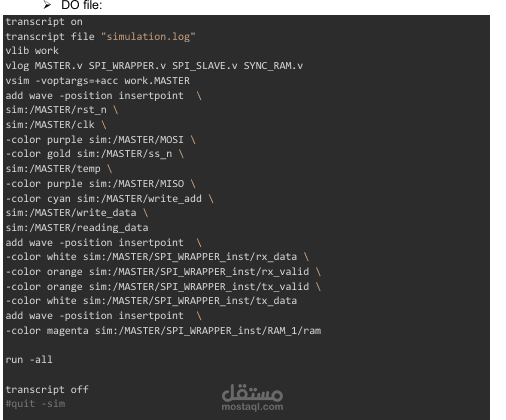

تنفيذ Simulation باستخدام QuestaSim

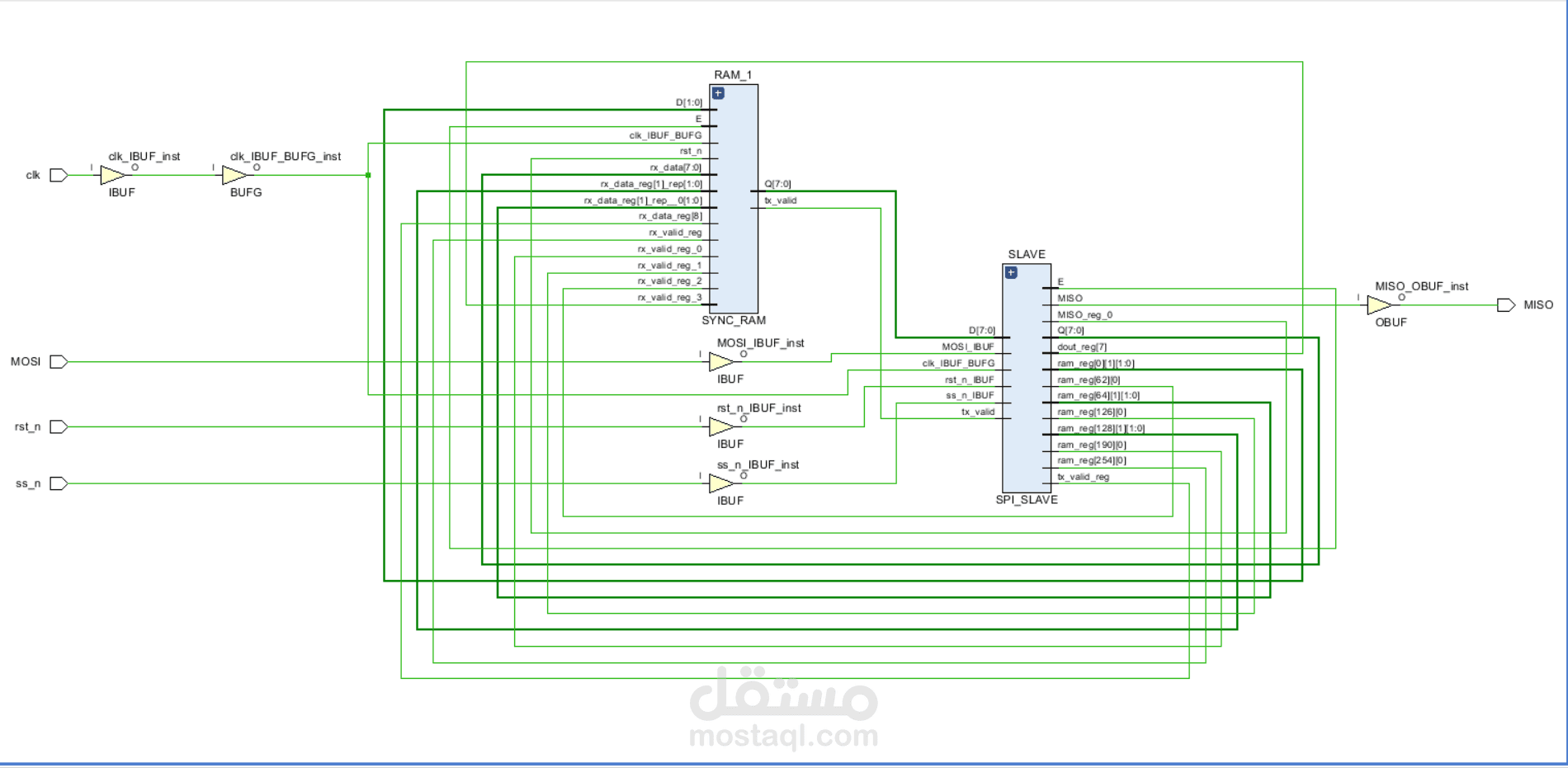

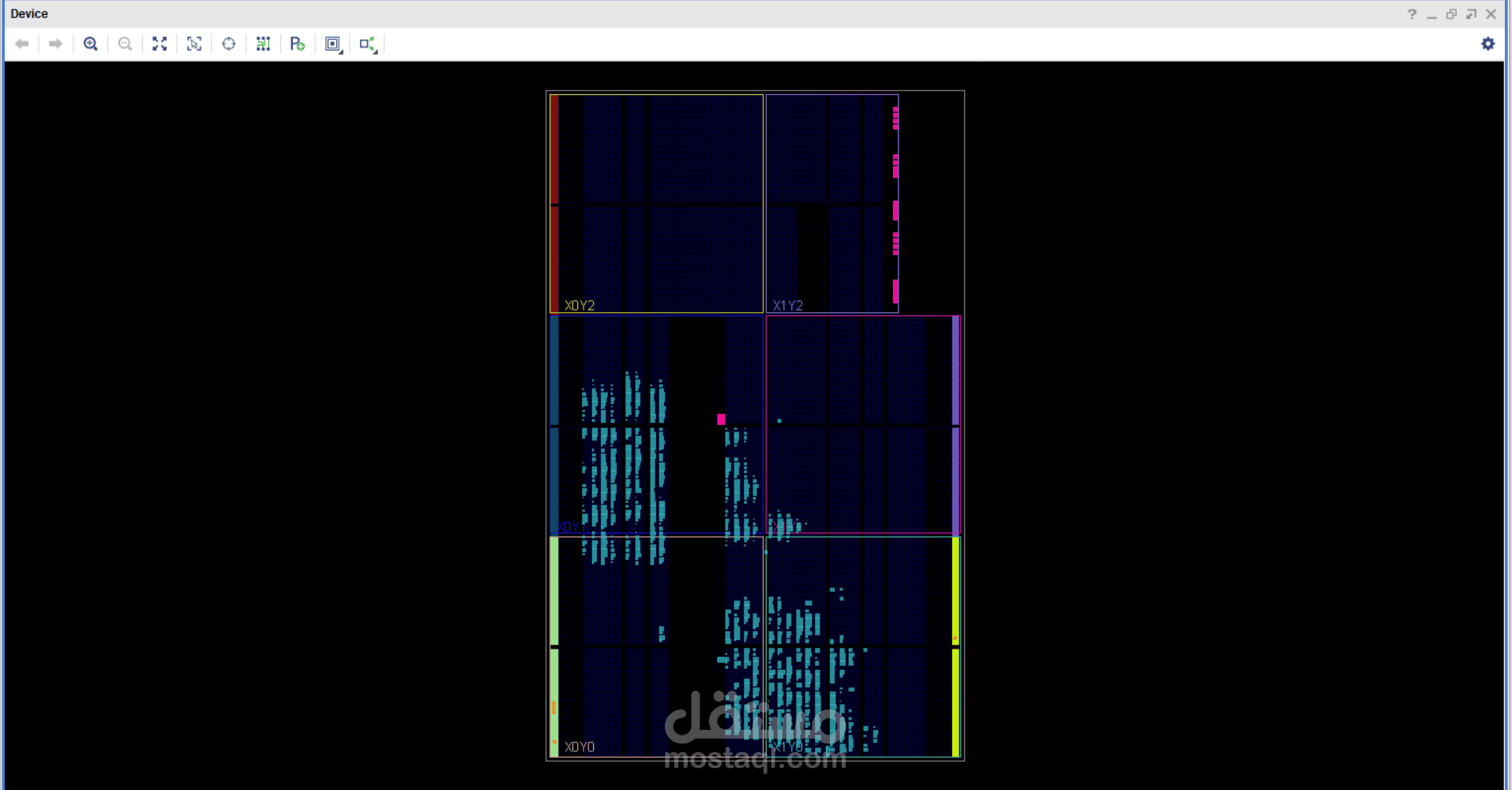

تنفيذ Synthesis و Implementation باستخدام Xilinx Vivado و Intel Quartus

تصميم RTL منظم قابل لإعادة الاستخدام والتوسع

تجهيز التصميم للتطبيق على FPGA