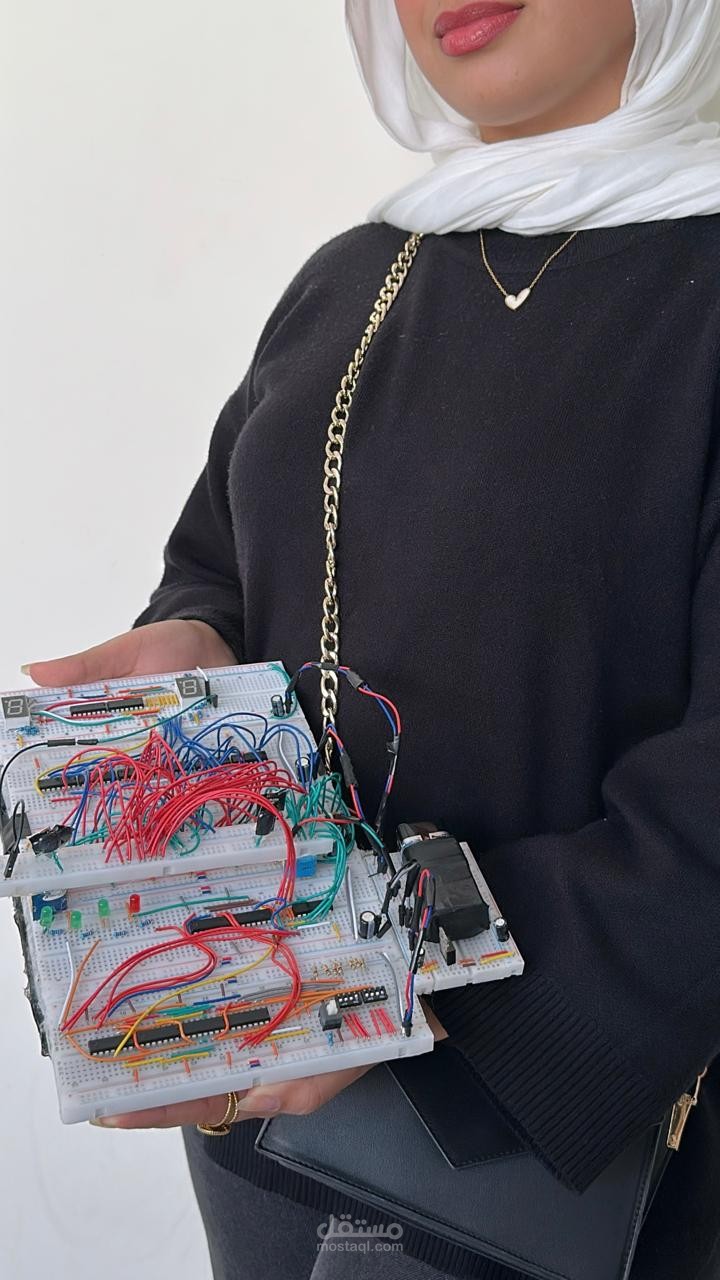

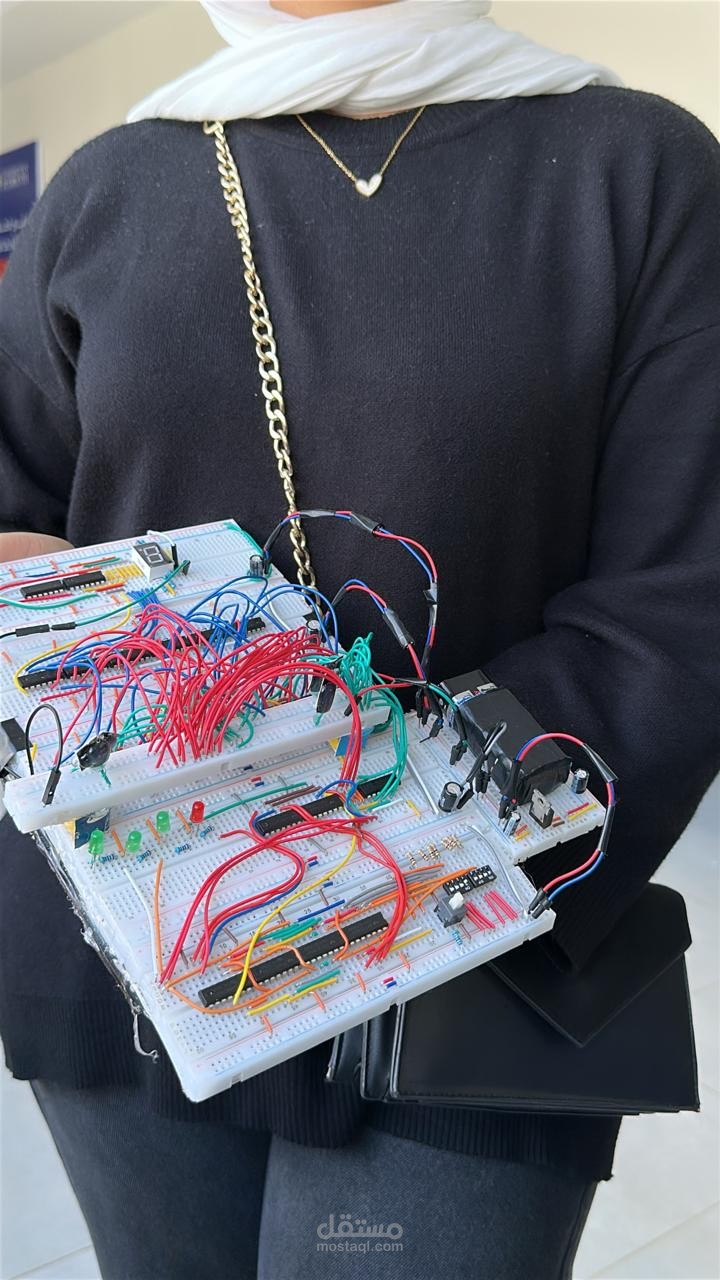

تصميم وتنفيذ وحدة حسابية 4-Bit (ALU) مع شاشة 7-Segment ومؤشر Even/Odd

تفاصيل العمل

هذا المشروع عبارة عن تصميم وتنفيذ دائرة 4-Bit ALU (Arithmetic Logic Unit) باستخدام دوائر TTL Logic ICs فقط، بدون استخدام أي Decoder IC جاهز.

المشروع يقوم بالوظائف التالية:

• تنفيذ عمليتي Addition و Subtraction باستخدام طريقة 2’s Complement

• تحويل الناتج الثنائي إلى صيغة Hexadecimal (0–F)

• عرض الناتج على شاشة 7-Segment Display

• إظهار حالة Even / Odd Parity باستخدام أقل عدد ممكن من البوابات المنطقية

تم بناء الجزء الحسابي باستخدام Ripple Carry Full Adders، بينما تم تصميم وحدة التحويل إلى Hexadecimal اعتمادًا على Karnaugh Map (K-Map) Optimization مع التحويل من POS إلى SOP لتقليل عدد البوابات المستخدمة وتحسين كفاءة الدائرة.

المكونات المستخدمة تشمل:

• 74LS86 (XOR)

• 74LS08 (AND)

• 74LS32 (OR)

• 74LS04 (NOT)

• 74LS11 / 74LS21

• Common Anode & Common Cathode 7-Segment Displays

ميزة المشروع أنه تم تنفيذ مؤشر Parity Indicator باستخدام الـ Least Significant Bit (LSB) فقط، بدون الحاجة لإضافة دوائر منطقية إضافية، مما يجعل التصميم أكثر كفاءة وبساطة.

تم اختبار الدائرة باستخدام Proteus Simulation بالإضافة إلى تنفيذها عمليًا باستخدام مكونات Hardware فعلية.

المشروع يعكس فهم عملي لـ Digital Logic Design، وتقنيات تبسيط الدوائر، وبناء أنظمة رقمية متكاملة قابلة للتطوير.