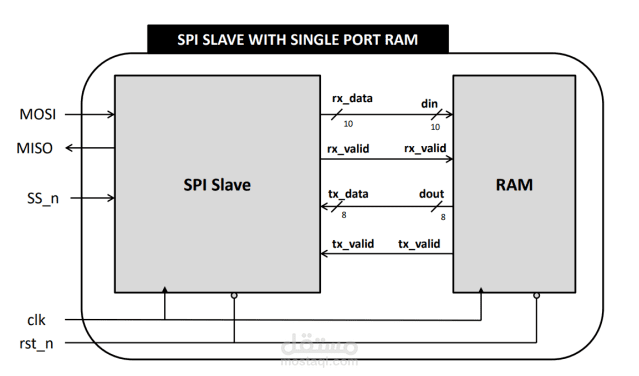

SPI SLAVE WITH SINGLE PORT RAM

تفاصيل العمل

هذا المشروع عبارة عن تصميم وتنفيذ وحدة SPI Slave مدمجة مع Single-Port Asynchronous RAM باستخدام لغة Verilog، مع دعم كامل للمحاكاة، التحقق الوظيفي، والتنفيذ على FPGA.

تم تنظيم المشروع بطريقة منهجية تشمل جميع مراحل دورة التصميم الرقمي، بداية من تصميم RTL، مرورًا بالمحاكاة والتحقق، وحتى التنفيذ الفعلي على الـ FPGA. يتضمن المشروع وحدات مستقلة لوحدة الاتصال عبر SPI، وحدة الذاكرة، بالإضافة إلى Top Module لدمج النظام بالكامل.

يحتوي قسم الـ RTL على:

- وحدة SPI Slave لمعالجة بروتوكول الاتصال التسلسلي

- وحدة Single-Port Async RAM لتخزين البيانات

- وحدة ربط عليا (Top-Level Integration Module)

- سكربتات لأتمتة المحاكاة على ModelSim / QuestaSim

- سكربتات لأتمتة عمليات Synthesis و Implementation على Vivado

بيئة التحقق تشمل Testbench كامل يحتوي على نماذج سلوكية وملفات تهيئة للذاكرة، مما يسمح باختبار التصميم تحت سيناريوهات تشغيل مختلفة، والتحقق من صحة عمليات القراءة والكتابة عبر واجهة SPI.

تم توليد Schematic Diagrams بعد مرحلة الـ synthesis لعرض البنية العتادية لكل وحدة على حدة، وكذلك النظام الكامل بعد الدمج، مما يساعد على فهم التركيب الداخلي وتحليل التصميم.

كما يشمل المشروع مخرجات FPGA النهائية مثل:

Constraint File

Netlist

Bitstream File

وذلك لدعم برمجة العتاد وتحليل استهلاك الموارد والتوقيت.

Single-Port Async RAM Module

توفر وحدة الذاكرة Single-Port Asynchronous RAM تخزينًا موثوقًا للبيانات مع دعم عمليات القراءة والكتابة من خلال واجهة بسيطة ومحددة:

ADDR: تحديد عنوان الذاكرة

DIN: إدخال البيانات للكتابة

WE: التحكم في عملية الكتابة

DOUT: إخراج البيانات من الذاكرة

تم تصميم الوحدة لتكون قابلة للتهيئة (Parameterized)، حيث تشمل:

MEM_DEPTH (الافتراضي 256) لتحديد عدد مواقع الذاكرة

ADDR_SIZE (الافتراضي 8 بت) لتحديد عرض ناقل العناوين

يسمح هذا التصميم بتكييف حجم الذاكرة بسهولة وفق متطلبات النظام.

يعكس هذا المشروع خبرتي في:

تصميم بروتوكولات الاتصال الرقمية

تصميم وحدات ذاكرة باستخدام RTL

التحقق الوظيفي باستخدام Testbenches منظمة

تنفيذ وتصحيح التصاميم على FPGA

بناء مشاريع جاهزة للتنفيذ العتادي والتحليل الزمني