DSP48A1 Project

تفاصيل العمل

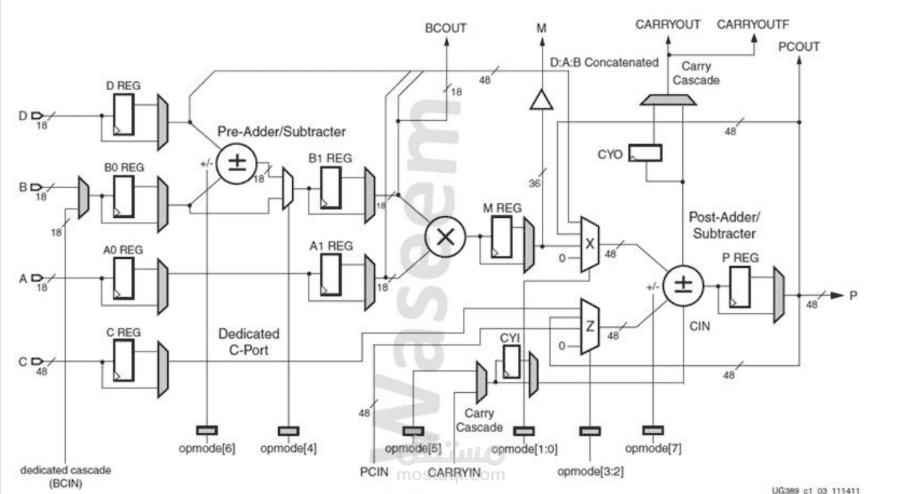

هذا المشروع عبارة عن تصميم وتنفيذ نموذج RTL كامل لوحدة DSP48A1 الخاصة بعائلة Spartan-6 FPGA من Xilinx، وهي واحدة من أقوى وحدات المعالجة الحسابية المخصصة لتطبيقات Digital Signal Processing عالية الأداء.

تم تنفيذ التصميم ليعكس بدقة البنية المعمارية لوحدة DSP48A1، مع دعم جميع الخصائص القابلة للتهيئة كما هو موضح في مواصفات Spartan-6، بما في ذلك مراحل الـ pipelining، التحكم في التسجيل، وإشارات التحكم الحسابي.

يشمل التصميم الوحدات الوظيفية التالية:

Input Pipeline Registers لإشارات A، B، C، D، CARRYIN و OPMODE

Pre-Adder/Subtracter لتنفيذ الجمع أو الطرح قبل مرحلة الضرب

Multiplier (18×18 → 36-bit)

Post-Adder/Subtracter بعرض 48-bit لدعم عمليات الجمع، الطرح والتجميع

Cascade Interfaces (BCIN/BCOUT و PCIN/PCOUT) لربط عدة وحدات DSP

Register Stages داخلية مثل MREG و PREG لتحسين الأداء الزمني

تم الالتزام بالتفسير الدقيق لإشارات OPMODE، وسلوك الـ reset، والتحكم في الـ carry، مع دعم جميع أوضاع التشغيل الأساسية للوحدة.

للتحقق من صحة التصميم، تم تطوير Directed Testbench يغطي جميع الأنماط التشغيلية لوحدة DSP48A1 باستخدام أنماط اختبار مدروسة، مع محاكاة كاملة على QuestaSim وتحليل نتائج الـ waveform. كما تم إعداد DO file لأتمتة عملية المحاكاة.

بعد الانتهاء من التحقق الوظيفي، تم تنفيذ مراحل:

Synthesis و Implementation باستخدام Vivado

فحص المخططات (Schematic Inspection)

تحليل التوقيت (Timing Analysis)

تقارير الاستهلاك (Utilization Reports)

Linting لضمان تصميم نظيف وخالٍ من الأخطاء

يوضح هذا المشروع خبرتي في:

- تصميم وحدات DSP منخفضة المستوى باستخدام RTL

- التعامل مع FPGA architecture و vendor-specific blocks

- بناء تصاميم عالية الأداء مع مراعاة التوقيت والموثوقية

- تنفيذ دورة تصميم رقمية كاملة من RTL حتى implementation