32-bit MIPS

تفاصيل العمل

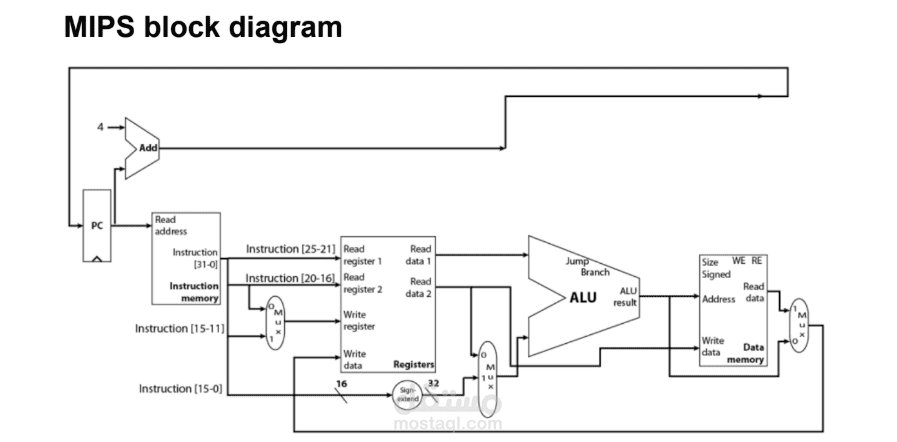

هذا المشروع عبارة عن تصميم وتنفيذ معالج MIPS 32-bit Single-Cycle باستخدام لغة Verilog، مع محاكاة كاملة على QuestaSim، قادر على تنفيذ برنامج مبني على مجموعة تعليمات MIPS ISA.

تم دعم وتنفيذ التعليمات الأساسية من نوعي R-type و I-type، والتي تمثل الأساس لمعظم لغات التجميع، مع التركيز على التنفيذ الصحيح للعمليات الحسابية والمنطقية والتحكم في تدفق البرنامج.

يدعم المعالج العمليات التالية:

العمليات الحسابية: Add، Subtract، Multiply

العمليات المنطقية: AND، OR، NOR، NAND

عمليات الإزاحة: Shift Left Logical، Shift Right Logical

عمليات المقارنة: Set Less Than، Set Greater Than، Set Not Equal

التعامل مع الذاكرة: Load Word، Store Word

التحكم في التدفق: Branch Equal

يتكون التصميم من الوحدات الأساسية التالية:

Program Counter (PC)

Instruction Memory

Control Unit

Register File

Arithmetic Logic Unit (ALU)

Data Memory

تم تنفيذ كل وحدة كوحدة مستقلة (Modular Design) ثم ربطها داخل Top Module، مع كتابة Testbench شامل للتحقق من صحة التنفيذ لجميع التعليمات المدعومة، وتحليل نتائج المحاكاة للتأكد من صحة الوظائف والتوقيت.

يوضح هذا المشروع قدرتي على:

- تصميم أنظمة رقمية متكاملة باستخدام RTL

- فهم وتنفيذ Computer Architecture عمليًا

- كتابة كود منظم وقابل للتوسع

- التحقق الوظيفي للتصميم باستخدام Simulation