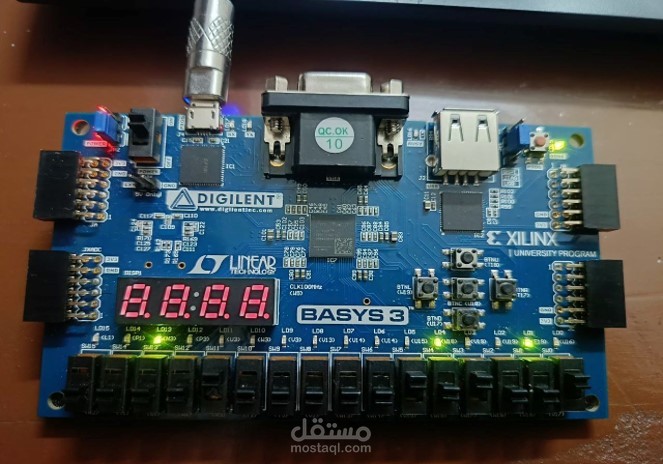

تصميم وتنفيذ ALU مخصص على FPGA (Basys 3) باستخدام Verilog

تفاصيل العمل

⚙️ تصميم وتنفيذ ALU مخصص على FPGA (Basys 3) باستخدام Verilog

قمت بتصميم وتنفيذ وحدة حسابية ومنطقية (ALU) مخصصة على لوحة FPGA من نوع Basys 3، باستخدام لغة Verilog HDL، مع التركيز على الدقة، الأداء، ومعالجة الحالات الخاصة (Exceptions).

? العمليات المدعومة داخل الـ ALU

الجمع (Addition)

الطرح (Subtraction)

الضرب (Multiplication)

القسمة (Division)

عمليات الإزاحة (Shift Left / Shift Right)

? إدارة الحالات (State & Status Registers)

لم يقتصر التصميم على تنفيذ العمليات فقط، بل شمل أيضًا نظام State Register لعرض حالات التشغيل والأخطاء، مثل:

Divide by Zero (القسمة على صفر)

Overflow (تجاوز السعة الحسابية)

حالات تشغيل أخرى توضح حالة ناتج العملية

? مميزات المشروع

ALU مصمم خصيصًا (Custom ALU) وليس استخدام IP جاهز

كتابة Verilog بشكل منظم وقابل للتوسعة

التعامل مع الأخطاء الحسابية بشكل احترافي كما في المعالجات الحقيقية

قابل للدمج داخل Processor أو CPU Design مستقبليًا

مناسب للتطبيقات التعليمية والأنظمة المضمنة (Embedded Systems)

? هدف المشروع

محاكاة طريقة عمل الـ ALU داخل المعالجات الحقيقية، مع فهم عملي لكيفية تنفيذ العمليات الحسابية والمنطقية، وإدارة الحالات الحرجة على مستوى العتاد (Hardware Level) باستخدام FPGA.