UART Design and Implementation using Verilog on FPGA

تفاصيل العمل

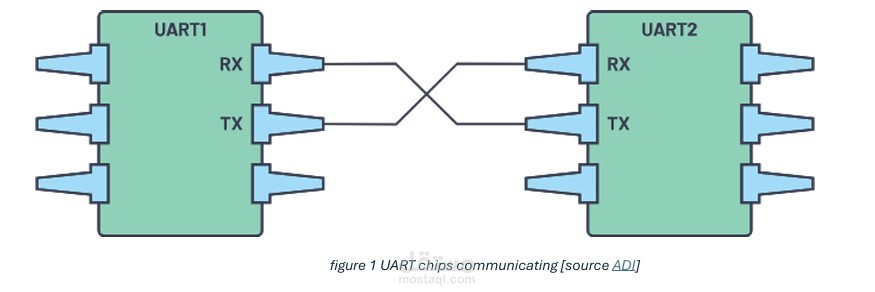

Designed and implemented a Universal Asynchronous Receiver/Transmitter (UART) module using Verilog HDL, targeting Spartan-6 FPGA.

The project focused on reliable serial communication, supporting configurable baud rate, start/stop bits, and data transfer between FPGA and external devices.

Key highlights:

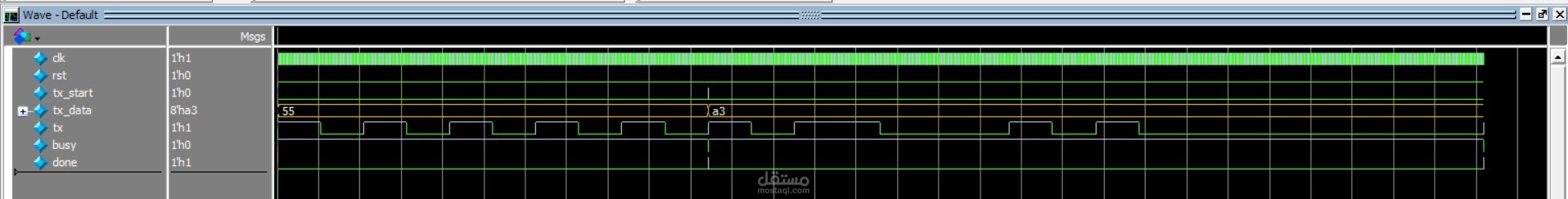

Developed using Finite State Machine (FSM) for control logic.

Verified functionality through ModelSim/QuestaSim simulations.

Tested on Spartan-6 hardware to validate real-time operation.

Ensured accurate transmission and reception with proper synchronization.