RTL to GDS Implementation of Low Power Configurable Multi Clock Digital System

تفاصيل العمل

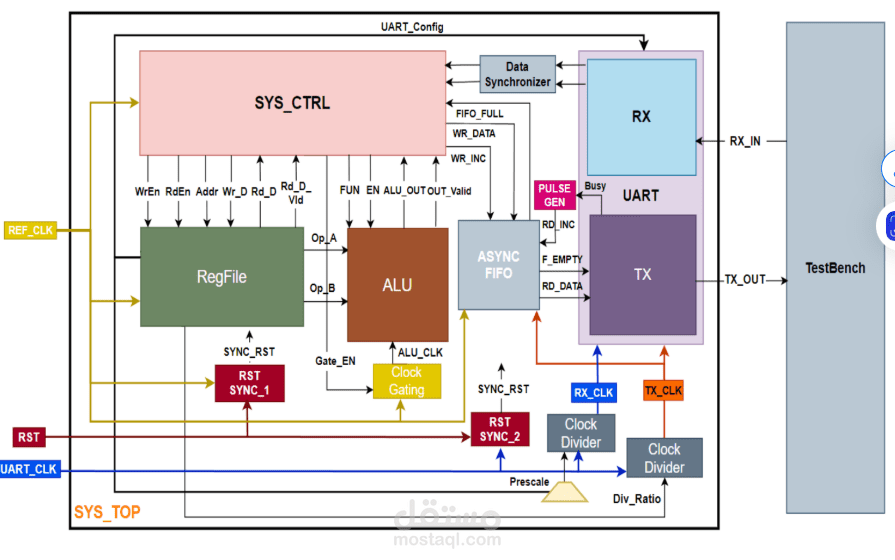

t is responsible of receiving commands through UART receiver to do different system functions as register file reading/writing or doing some processing using ALU block and send result using 4 bytes frame through UART transmitter communication protocol

Designed system blocks (ALU, Register File, Asynchronous FIFO, Clock Divider, Clock Gating, Synchronizers, UART) from scratch in Verilog. Integrated and verified functionality using a self-checking testbench. Synthesized and optimized the design using Synopsys Design Compiler, fixing timing violations